# Pulsonix Version 12.0 Update

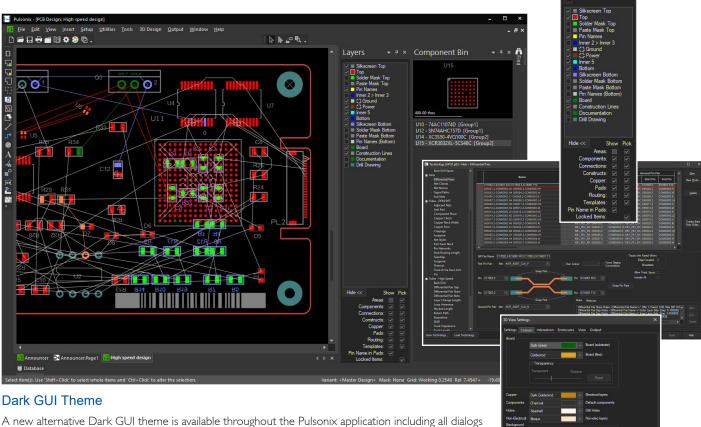

and message boxes within it. Easily switchable between Light and Dark themes, it is complimented with new toolbar icons which are distinguishable against contrasting backgrounds of the modes. The Dark theme makes professional working with Pulsonix for long periods of time much less stressful on the eyes and mind, and reduces fatigue, therefore increasing productivity.

### Core Technology Advancements

#### Redeveloped with a 64-bit architecture

Pulsonix has been redeveloped as a true 64-bit application. Utilising the 64-bit architecture, Pulsonix performance has increased meaning a higher efficiency for larger designs. The existing 32-bit address space memory limitation of 4Gb has been increased with 2Tb+ now available.

#### Additional Multi-threading Technology

Multi-threading technology to utilise multi-core processors already exists within Pulsonix but has been further expanded to include: Find Part in Library, Find on the Insert Component option, Library Indexing, interrupt for design clearances and STEP file generation. These options will benefit from much more efficient parallel processing of data achieving results up to 50% faster.

# www.pulsonix.com

### **3D STEP Preview**

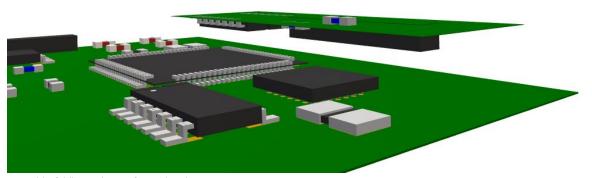

#### Multiple Board capability within STEP Preview

From within the Pulsonix PCB design environment, you can now define multiple boards for processing in the STEP environment. Additional

board origins, axis points, offsets, rotations and board references can now be added to the boards within the PCB design editor. The boards can then be passed through and subsequently annotated in 3D to show their final positions once fully assembled.

Commands in the STEP Previewer enable folding to be performed and the resultant board positions displayed. Clash detection can be run between each board in any orientation with component position refinement performed to remove the errors. Component placement is back annotated to the 2D PCB designs.

Multi-board capabilities in the 3D environment means adjacent boards can be positioned and clash detection run

#### New 3D Design menu

A new 3D Design menu has been added to bring all aspects of the 3D STEP functionality together in one convenient location.

#### Multi-threading capability for STEP file generation

STEP file generation now uses multi-threading to significantly speed up file creation. Components and design data from the Advanced Settings are processed in parallel taking advantage of multiple processor cores.

#### Cross Probing between PCB and STEP Preview

Bi-directional cross probing has been added to Pulsonix V12. Two new modes will enable Cross Probe in each direction between 2D PCB and the 3D views. Probing can be achieved between components and design items in each environment.

#### **Override Clash Detection**

Clash detection can be explicitly overridden where you have situations where you want items to touch, for example, where a plug on the moving board fits into a socket on the static board. To facilitate this, a new attribute, 3DIgnoreClash, can be used. This will be added to a pair of components that will be potentially violated. When the Clash Detection option is then run, the component will be ignored.

| Tools | 3D Design Output Window Help                                      |

|-------|-------------------------------------------------------------------|

|       | 🔂 3D Settings                                                     |

|       | 🗞 3D Viewer Colours                                               |

|       | 🐾 Setup STEP Models Folder                                        |

|       | 🖉 Import STEP Board                                               |

|       | $\hat{\mathbf{r}}_{\underline{I}}^{-}$ Generate Heights from STEP |

|       | 💼 Save STEP Models                                                |

|       | 🌏 Add Cases/Enclosures                                            |

|       | 👕 3D Viewer                                                       |

|       | 😭 Output STEP File                                                |

|       | ा Import STEP Component Positions                                 |

The new 3D Design menu brings all aspects of MCAD integration into one convenient location

# www.pulsonix.com

#### New Up-front DFM Rules Definitions

Within the Technology dialog, significant improvements have been made to the design definition and verification routines with the addition of many new DFM rules.

New rules have been added for: Min Pad Land for Mounting Holes, Min Text Size Rule, Min Solder Mask Width Rule, Solder Mask To Track Rule, Define Teardrop by Length, Min Copper Spacing for Tab Routs and V-Scores in Panel Editor and a Copper Pour rule to 'Keep Touching Copper of the same net'.

#### New Component Colour Rule

A new rules dialog enables colouring of components based on many criteria, such as number of pins, Component Name, Attribute Name, Symbol Name and suchlike. This means a set of two-pin components in the Schematic design can be filled with a colour for example. It also enables components within an area on a certain layer to be coloured in the PCB, such as the Assembly layer, which would then make it easier to read once printed.

#### New High-Speed Design Rules

New rules added to the Technology dialog enable more refinement when designing critical high-speed circuits.

The Anti Pad dialog is used to define the rules used to generate additional copper plane cutouts on layers below pads (or vias, mounting holes, etc). When copper is poured, or a powerplane generated, these cutouts are applied. The rules dialog allows the cutouts to be autogenerated and is necessary to avoid parasitic capacitance. In some cases, the whole component area needs a cutout, the rules page allows this. Match Pair Spacings are now available for Differential Pairs, Signal Paths and Sub Nets.

The Track Mitring Rule defines whether the 'mitre' should be curved and/ or filleted once routed.

Additional high-speed rules can be used to define Loop Antennae, Stub Routing Length and Return Path.

The Copper Check Rule enables copper 'slivers' to be declared and checked. These long, thin, dangling sections of copper can cause issues during manufacturing. When creating high frequency designs, can then also act as a net antenna at certain frequencies and therefore should be removed.

New rules for SMD To Corner and SMD To Plane enable additional precision for High-Speed nets.

#### New Advanced Shapes

New advanced shape types have been added to enable the creation of Splines, Ellipse and Waves. The shapes can be added using underlying mathematical algorithms with a simple user interface to control them. Once inserted, interactive features further enable their editing and manipulation.

#### Feature Summary:

- Change Part Type of an Associated Part

- Same Symbol filter in Change Part Dialog

- Highlighted hyperlinks on Part Browser

- Highlighted hyperlinks on Insert Component dialog

- Highlight Colour for Components Not Fitted in any Variant

- Delete Unused or Unfitted Components in Variant Manager

- Preserve block instance variant on Reload Block

- Override Land Suppression on individual Pads and Vias

- New Pour All Templates Command

- Change 'open' Copper to Track and vice versa

- Area Mounting Hole Keep Out/In

- Match Rotation/Mirror of previous Component from Bin

- New 'Replicate Shape As' feature

- Highlight Net includes Star Point

- Redesigned Toggle Layer dialog

- New in-build attribute of <Not Fitted In>

- Attribute Validation when adding a Component

- New DRC Silkscreen Overlap Doc Shapes

- New DRC Check for Modified Templates

- Type Final Position in Apply Layout Pattern

- New Set PCB Panel Origin Command

- Plot and Combine PCB/SCM designs in PDF Export

- Selectable Hyperlinks in PDF Export

- Pulsonix 12.0 is fully supported under Windows 11

#### Pulsonix

20 Miller Court, Severn Drive, Tewkesbury, Glos, GL20 8DN, UK Tel: +44 (0) 1684 296 551 Email: info@pulsonix.com Web: www.pulsonix.com Copyright (C) WestDev Ltd 2022. All rights reserved. E&OE. All trademarks acknowledged to their rightful owners